Проведя небольшой поиск в «отечественном» инете, и не обнаружив сообщений о применении так называемых «Систем на кристалле» - PSoC - при построении SDR приемников, хочу познакомить коллег с небольшой публикацией под названием

«A Simple SDR Receiver» или «Простой SDR приемник»

Разумеется в вольном переводе и с некоторыми сокращениями и рядом добавлений, не мешающими, на мой взгляд, восприятию сути изложенного.

Автор статьи американский радиолюбитель из Калифорнии Michael Hightower (KF6SJ). С авторским текстом можно познакомиться в оригинале по адресу: http://www.tapr.org/pdf/DCC2010-simpleSDR-KF6SJ.pdf

Предисловие:

С появлением программируемых систем на кристалле разработчики получили мощный инструмент для проектирования -«систему на кристалле - PSoC» по цене 8-битного микроконтроллера. В чипах PSoC встроены массивы аналоговых и цифровых блоков, на порядок более функциональных, чем фиксированная периферия. Такие стандартные элементы микроконтроллеров как АЦП и ЦАПы, таймеры, счетчики, ШИМы, UART легко реализуются в PSoC. В изложении KC6SF речь идет о PSoC фирмы Cypress Logic.

Для справки. Элементы обычно не входящие в состав 8-битных микроконтроллеров, такие как: фильтры, усилители, генераторы случайных чисел также можно разместить в этих чипах. Таким образом, одна микросхема PSoC заменяет несколько компонентов схемы построенной на стандартных микроконтроллерах. Все функции, внутренние соединения, внутренняя конфигурация, и даже контакты ввода-вывода перепрограммируются пользователем.

Более того, непосредственно во время работы чипа PSoC можно динамически менять внутренние ресурсы, получая при этом функционально новую систему.

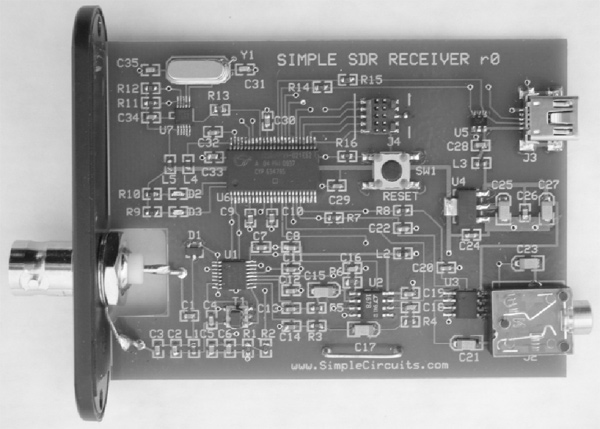

Рис.1. Простой SDR приемник (SDR - software defined radio, PSoC - programmable system-on-chip).

KF6SJ продолжает;

... «Лень - некий актив для инженера. Уменьшение числа компонентов в проекте снижает конструктивный объем, собственно приобретение элементов и, что наиболее важно, уменьшает его стоимость. Будучи от природы ленивым инженером, я хочу, чтобы мои проекты имели минимум компонентов настолько - насколько это возможно. Но! без потери качества, и обладали простотой конструкции.

В течение ряда прошлых лет я соорудил несколько доморощенных SDR приемников, с использованием программного обеспечения. Причем каждый последующий проект становился проще, лучше и дешевле. А количество используемых компонентов было существенно меньше, чем в предшественнике.

Один из моих любимых компонентов - серия Cypress Semiconductor - PSoC. Эти м/с намного интереснее, чем обычные микроконтроллеры; они поддерживают программное обеспечение для конфигурирования внутренней структуры, аналогичной той, которая сопутствует системам с использованием однокристальных схем - аналоговой и цифровой периферии. Это семейство микросхем PSoC, называемых программируемой системой на кристалле. Новейшая серия от Cypress Logic - CY8C3xxx, содержит 67 МГц микрокомпьютер класса 8051, аналого-цифровой преобразователь (АЦП) достаточно быстрый для реализации SDR-приемника, и обладает другими ценными функциями, которые весьма желательны при проектировании SDR приемника. Когда я только увидел эти элементы, то у меня возникла идея реализовать их в своем новом КВ-приемнике.

Цель создания приемника:

Моя цель состояла в том, чтобы использовать PSoC кристалл новой серии в качестве краеугольного камня SDR приемника. Свой приемник я не планировал наделить высочайшими характеристиками, это приемник для обычной работы в эфире, а не для серьезного серфинга по DX. Не следует ожидать от него каких-либо выдающихся характеристик. Главное, что он должен содержать минимально возможное число малогабаритных элементов, удобных в сборке. Я также полагаю, что добавление ЖК-экрана, средств управления и настройки частоты в данном приемнике только увеличит конструктивный объем и его стоимость. (Но вовсе не исключает их появление в других проектах, прим. RW3AY).

Поэтому будет лучше, если для ввода данных будет использоваться персональный компьютер. Так как у PSoC есть встроенный USB порт, приемник можно соединить с PC обычным USB кабелем, обеспечить не только управление, но и его питание из того же USB разъема, экономя при этом не только на самом разъеме, но и на источнике питания! Управление приемником через USB порт мало чем отличается от управления через стандартный COM-порт. В качестве управляющей программы подойдет «The Ham Radio Deluxe (HRD)», которая полностью обеспечит управление данным радиоприемником.

Основной SDR приемник:

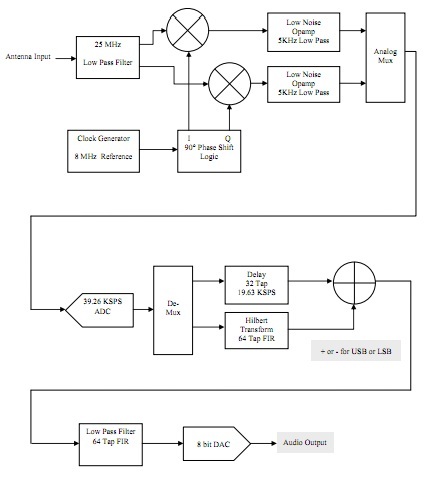

Собственно сам SDR приемник построен с использованием метода квадратурного преобразования частоты, как показано на блок-схеме рис.2. Данный метод предполагает наличие аналоговых коммутаторов, работающих в определенной последовательности, для реализации которой требуется опорная частота (гетеродин) в два или четыре раза выше входной частоты приема для каждого конкретного диапазона. Четыре выхода аналогового квадратурного преобразователя 0, 90, 180, и 270О отфильтровываются и усиливаются парой ФНЧ (фильтров нижних частот) на операционных усилителях. (В данном случае это мало чем отличается от большинства известных простых схем, прим, RW3AY). А, вот, послеоперационная обработка обеспечивается в PSoC микрокомпьютере, с использованием цифровых методов обработки.

В данном случае обработка производится без использования звуковой карты за счет преобразования аналогового квадратурного сигнала в цифровую форму, при этом будет удалена (существенно ослаблена, прим. RW3AY) нежелательная боковая полоса, проведена соответствующая фильтрация и обратное преобразование из цифровой формы в аналоговый аудиосигнал. (Подключайте наушники и наслаждайтесь эфиром, прим. RW3AY).

Figure 2: Аппаратно-программная структура SDR приемника.

См. http://www.tapr.org/pdf/DCC2010-simpleSDR-KF6SJ.pdf

Low Noise Opamp

5KHz Low Pass

25 MHz Low Pass Filter

Analog Mux-DeMux 39.26 KSPS

ADC Clock Generator 8 MHz Reference

I / Q -- 90° Phase Shift

Logic Delay - 32 Tap 19.63 KSPS

Hilbert Transform - 64 Tap FIR

Low Pass Filter - 64 Tap FIR

8 bit DAC

Low Noise Opamp

5KHz Low Pass

+ or - for USB or LSB

Audio Output

КРАТКОЕ ОПИСАНИЕ РАБОТЫ

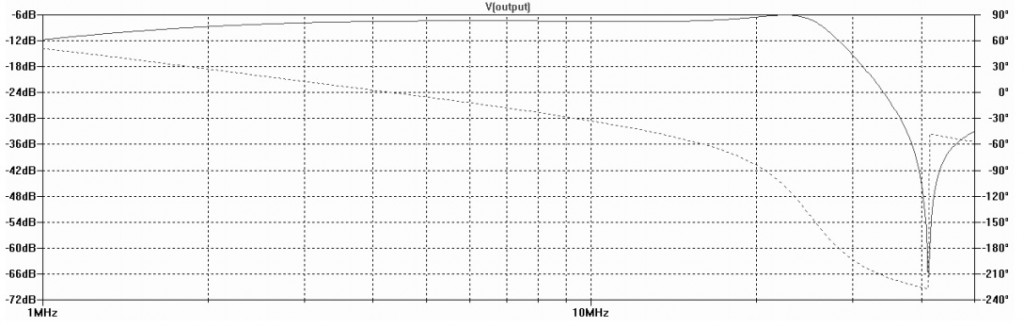

Во входной цепи со стороны антенны установлен фильтр нижних частот, имеющий частоту среза 25 МГц. На рис.3 показана частотная характеристика данного фильтра.

Рис. 3: АЧХ входного ВЧ фильтра (Input RF Filter Response).

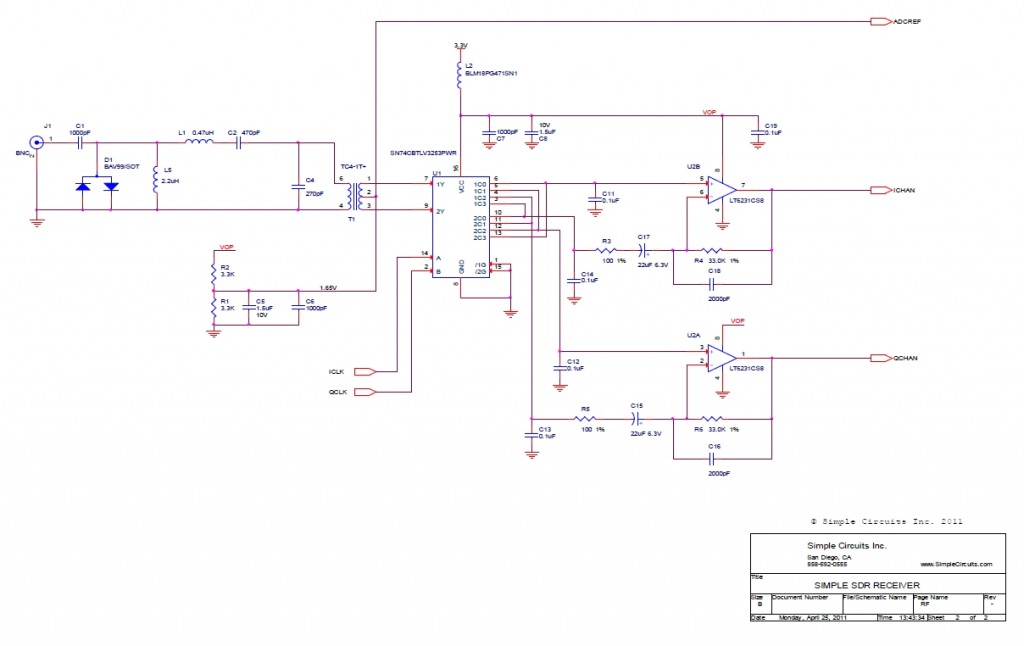

Что касается схем на рис.6 и рис. 7, то микросхема U1 (IDT74CBT или LV3253PGG - сдвоенный 1 на 4 multiplexer/demultiplexer), используется в качестве смесительного детектора. Данный процесс подобен работе аналогового гетеродинного смесителя, управляющие и выходные сигналы которого соответствуют цифровым логическим уровням.

Чип тактового генератора (Cirrus Logic clock generator ) - микросхема U7 (CS2100-CP ) используется в качестве генератора тактовой частоты. Следует отметить, что это не просто генератор на какую-то фиксированную частоту (см. даташит http://www.cirrus.com/en/pubs/proDatasheet/CS2100-CP_F1.pdf). Данная м/с соответствует классу «Fractional-N Frequency Synthesizer and a Digital PLL». (Заранее извиняюсь за не совсем точный перевод, RW3AY). Фактически это Delta-Sigma перемножитель с фазовой подстройкой частоты. Управление им (установка частоты) производится Cirrus Logic микроконтроллером U6 (см. принципиальную схему).

(На этом рисунке приводится структура м/с CS2100-CP. Добавление от RW3AY).

Преимущество этого элемента в том, что в данном случае он по своему функциональному назначению соответствует цифровому синтезатору (DDS), но значительно дешевле. К тому же элемент обладает небольшим фазовым джиттером (дрожанием фронта импульса). В то же время его выходной сигнал логического уровня, поэтому он может быть непосредственно связан с входами мультиплексора (смесителя) без применения дополнительного компаратора. Удобно, не правда ли?

Тактовый генератор вырабатывает вдвое большую частоту. А уже PSoC обрабатывает его таким же способом, как это делается в простом SDR приемнике для получения квадратурных I-Q сигналов, сдвинутых друг относительно друга на 90°.

Спецификация PSoC гарантирует ее работу по входу до частоты 33 МГц. Это означает, что входная частота собственно приемника будет ограничена в верхней границе принимаемого диапазона частот. Гарантируемая верхняя частота составит 16.5 МГц. Однако, после тестирования нескольких приемников, можно утверждать, что все они были работоспособны, по крайней мере, до 18 МГц (при тактовой частоте до 36 МГц), или почти до 17-метрового любительского диапазона.

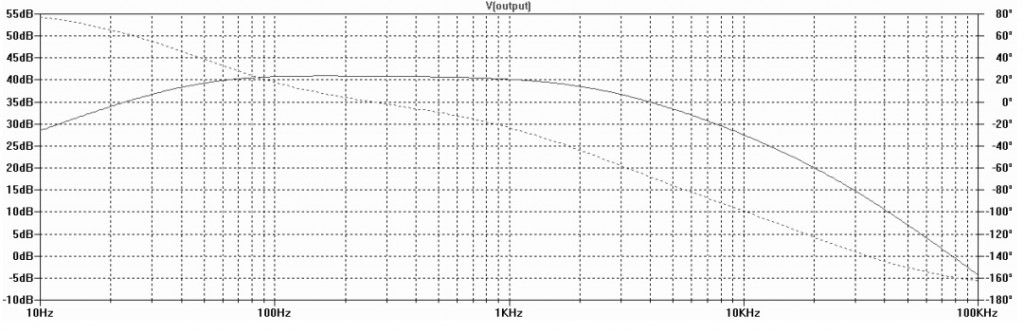

После смесителя RX, как это обычно делается в рядовом SDR приемнике, следует пара ФНЧ, собранных на малошумящих операционных усилителях U2A и U2B (LT1678CSS). Они выбраны исключительно из-за низкого уровня шума и способности работать по входу / выходу вблизи потенциалов питания и земли (rail to rail).

Входная чувствительность операционного усилителя, как правило, находится в пределах нескольких микровольт. Так как усиление ОУ на частоте 1 кГц почти 40 дБ, выходные сигналы будут находиться в диапазоне от нескольких сотен микровольт до десятков милливольт. ФНЧ на ОУ - это только первый этап фильтрации - имеет частоту среза 3 кГц. На рис.4 изображена частотная характеристика операционного усилителя.

Рис. 4. АЧХ ФНЧ на операционном усилителе (Op amp circuit frequency response).

Вся дальнейшая обработка сигнала после НЧ фильтрации обеспечивается в цифровой области м/с U6 - PSoC микроконтроллером (CY8C3866PVI).

К сожалению м/с U6 содержит всего один аналого-цифровой преобразователь (АЦП). А обрабатывать приходится два основных канала I и Q. Поэтому для подключения к АЦП приходится задействовать аналоговый мультиплексер. Исходя из технических характеристик PSoC, и встроенного 14-битного АЦП полоса Nyquist составляет почти 10 кГц. АЧХ (рис.4) на частоте 10 кГц имеет завал почти на 15 дБ. Это не очень сильно проявляется при прослушивании, но оставляет «открытой дверь» для усовершенствования в будущей версии.

В остальном «все отдано на откуп» цифровой обработке. PSoC состоит из 3-х основных частей, первая их которых называется «digital filter block» или DFB - блок цифрового фильтра. В целом это встроенный DSP модуль, работающий независимо от внутреннего 8051 процессора. Это специализированный программируемый 24-разрядный DSP фильтр или его еще называют аппаратным акселератором. С его помощью реализуется и оптимизируется построение FIR фильтра. (Здесь я пропускаю математические выкладки, характеризующие процессы фильтрации, формирование необходимых задержек, переворотов фазы, преобразования Hilbert и т.п., сопутствующее удалению нежелательной боковой полосы. Подробности смотрите в оригинале статьи, прим RW3AY).

В конечном итоге выделенная боковая полоса, т.е. ее представление в цифровом виде, обрабатывается узкополосным цифровым фильтром нижних частот. Данный фильтр уже имеет очень крутой скат на частоте 2 кГц, что и показано на рис.5. Как вы понимаете, - это основное преимущество цифровой обработки по сравнению с аналоговой фильтрацией. Особенно впечатляет стабильность характеристик при повторении и способности работы в широком диапазоне температур. Это основные причины чтобы использовать цифровую обработку. (Не говоря уже о других, прим.RW3AY).

После цифровой фильтрации в работу вступает один из 8-битных цифро-аналоговых преобразователей (ЦАП) PSoC, с помощью которого поток данных преобразовывается обратно в аналоговый НЧ сигнал. Далее он буферируется сдвоенным операционным усилителем, U3.

Рис. 5: АЧХ цифрового ФНЧ (PSoC Digital low-pass filter response).

Управление приемником.

В PSoC имеется внутренний высокоскоростной USB порт. Для работы написана специальная программа, реализующая последовательный коммуникационный порт. При работе в связке с персональным компьютером, приемник представляет собой обычное устройство, подключенное к последовательному USB порту. Используя стандартные CDC драйверы (communication drivers), которые встроены в Windows, приемник, может находиться под управлением хорошо известной «проги» - Ham Radio Deluxe (HRD). Собственно приемник использует протокол связи трансивера Elecraft K2, который был выбран исключительно из-за его доступности и письменной спецификации.

Звуковой выход приемника может быть непосредственно подключен к наушникам с низким импедансом. Наушники должны иметь собственный регулятор громкости. Использование хороших компьютерных колонок, в которых есть встроенный усилитель и регулировка громкости, вообще идеально, т.к. в самом приемнике нет собственной регулировки громкости.

Радиоприемник работает в широком диапазоне частот от 3.5 МГц и по крайней мере до 18 МГц (от 80 до 17 метров).

Используя программу HRD можно пользоваться любой из 4 полос пропускания ФНЧ: FL1 - фильтр нижних частот 2.5 кГц, FL2 - фильтр нижних частот 2.0 кГц, FL3 - фильтр нижних частот 1.5 кГц, и FL4 для CW и RTTY - полосовой фильтр 1.0 кГц, и 400 Гц с полосой (+/-200 Гц).

Кнопка аттенюатора (АТТ) уменьшит громкость на несколько децибел.

Основная характеристика MDS:

Так вот в данном приемнике MDS равен -117дБм. Типичный приемник обладал бы несколько большей величиной -120дБм. Однако, на нижних диапазонах, где атмосферные помехи весьма велики, этого более чем достаточно. Фактически, в сравнении с FlexRadio-3000, трудно определить большое различие. На мой взгляд, неплохо для приемника за $50.

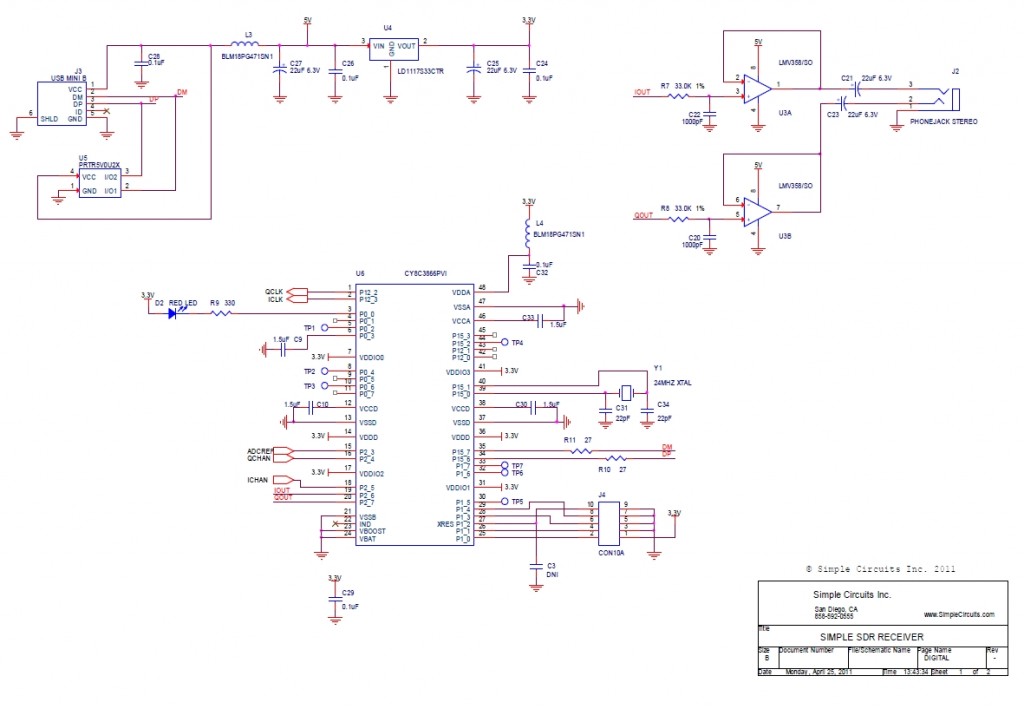

Рис. 6: SDR приемник, схема 1, ВЧ модуль.

Рис. 7: SDR приемник, схема 2, цифровая обработка.

Дополнение от RW3AY:

Я не очень сильно сократил данную статью, только в тех местах, которые указал в комментариях. В завершение привожу две принципиальные схемы RX, правда, качество их оставляет желать (потерялось при конвертации из одного формата в другой). Но в авторском варианте статьи в формате PDF они неплохо смотрятся, RW3AY.

К сожалению, автор не сопровождает свой материал программными выкладками, т.е. соответствующим софтом. Желающие расширить свой кругозор в области программирования систем на кристалле от компании Cirrus Logic обращайтесь к сопутствующей документации, и осуществляйте более расширенный поиск по рассматриваемой проблеме. Многое из того, что осталось как-бы за кадром, можно найти в сети. В частности, можно скачать ПО по программированию PSoC, которое мало чем отличается о программирования микросхем ПЛИС (графический редактор).

Не поленитесь и загляните на сайт компании Simple Circuits Inc., работником которой, по всей видимости, является KF6SJ: http://www.simplecircuits.com/SimpleSDR.html, откуда можно скачать ZIP архив 20 760 057 байт - SimpleSDR_RX_TAPR (1).zip. - обе схемы RX в достаточно хорошем качестве.

Микросхемы, применяемые автором в своем приемнике, по крайней мере, в Москве можно приобрести. Лично проверял, но надо побегать...

Специально для рубрики «КВ и УКВ»

Б.Родин RW3AY (февраль - апрель 2011 год).